## 2024 International Solid-State Circuits Conference

# (ISSCC) Review

숙명여자대학교 전자공학전공 정준원 교수

**Topic: Power**

### **Session 8: Hybrid DC-DC Converters**

Session 8에서는 inductive switching converter와 switched capacitor를 합친 hybrid 구조의 DC-DC converter가 11편 소개되었다. 높은 전력변환효율, 높은 전력밀도, 빠른 과도응답, 높은 입력 전압 달성 등이 Session 8에 수록된 논문들의 주된 목표이다.

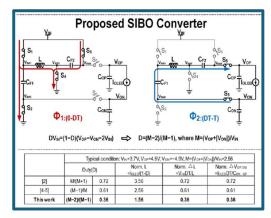

[그림 1] (좌) SIBO converter와 <#8.1>, (우) buck-boost converter의 <#8.2> power stage

#8.1은 AMOLED 용 single-inductor bipolar-output (SIBO) 변환기를 소개했다. 기존 state-of-the-art SIBO 기술 대비 전력변환효율이 7% 상승했고, die 면적 기준 전력 밀도는 2배 상승했다. 뿐만 아니라 요구되는 인덕터 값을 2.2 μH로 줄였으며, 출력 리플 전압, 과도 응답 역시 기존 기술 대비 좋아졌다. Power stage에 기존 대비 flying 커패시터와 스위치를 하나씩 더 추가했는데, 이로 인해 듀티 사이클이 41% 줄어들어 결과적으로 인덕터 전류, 인덕터 전류 리플, 출력 전압 리플이모두 줄어들었다. Bipolar 출력을 common-mode 와 differential mode 로 나누어 제어하여 과도응답 특성을 향상시켰다.

#8.2 는 hybrid 방식의 buck-boost 변환기를 소개했다. 주된 특징은 Seamless 한 buck-boost 모드 변환과, 높은 전력변환효율이다. 이를 달성하기 위한 본 논문은 인덕터 양단에 Flying 커패시터 두 개를 대칭적으로 배치한 power stage 구조 (Bilaterally-symmetrical hybrid, BSH)를 제안했다. 이를 통해 기존 기술과 달리 flying 커패시터 전압이 입력 전압에 따라 연속적으로 변하여 seamless 한모드 변환이 가능하다. 또한 BSH 구조로 인해 buck 과 boost 모드 모두에서 인덕터 전류 저감이가능하여 높은 전력변환효율을 달성했다. 뿐만 아니라 모든 전력 스위치 양단 전압을 4.2 V이하로 내릴 수 있어 5 V CMOS TR을 이용해 전력 스위치 구성이 가능하다.

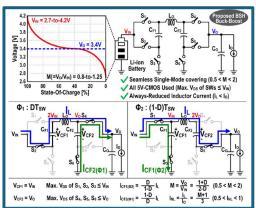

[그림 2] (좌) energy harvesting 용 PMU <#8.5>, (우) 고전압용 buck converter <#8.6>

#8.5 는 에너지 하베스팅용 전력관리시스템 (PMU)을 소개했다. 해당 PMU 는 6 nA 의 낮은 대기전류를 소모하고, 88000x dynamic range 의 전력을 출력한다. 90.1%의 높은 효율을 나타내며 인덕터 사이즈를 기존 기술 대비 90% 이상 저감시켰다. 대기전류 저감 및 효율 향상을 위해서 전력 스위치 구동 전압을 최적화, event-driven 기술을 적용, I/O standard 셀을 최적화, constant peak inductor current 방식을 적용했다. 인덕터 저감을 위해서 커패시터가 추가 적용된 hybrid power stage 를 제안했다. 이를 통해 인덕터 전압을 감소시킬 수 있기 때문에 인덕터 값을 줄일수 있다.

#8.7 은 고전압용 (12 V to 60 V) hybrid buck converter (1.2 V 출력)를 소개했다. 높은 전력변환효율 (최대 92.7%)을 얻었다. 뿐만 아니라 기존 고전압 converter 기술의 매우 높은 (혹은 낮은) duty cycle 문제, 입력 변화에 따른 flying 커패시터 전압 변동 문제, 느린 과도 응답 문제를 완화했다. 기존 고전압 converter 는 인덕터와 입력 사이에 switched-capacitor 를 배치한 것과 달리 본 논문에서는 인덕터와 출력 사이에 switched-capacitor 를 배치하는 serial-parallel-connected switched-capacitor (SPCSC) 기술을 제안했다. 따라서 switched-capacitor 에 저전압 전력 스위치 사용이 가능해져서 전력변환효율이 향상된다. 인덕터와 입력 사이에는 고전압 전력 스위치를 사용해야 하지만 SPCSC 구조 덕분에 인덕터 전류가 저감 되기 때문에 전력변환효율에 미치는 영향이 크지 않다. 해당 switched-capacitor 의 flying 커패시터 전압은 최종 출력 전압의 배수로 설정하여 입력 dependency 를 완화했다. 또한, Switched capacitor 를 통해 부하를 공급하기 때문에 과도응답 특성이 개선된다.

#### **Session 28: High-Density Power Management**

Session 28에서는 높은 전력밀도의 LDO, inductive DC-DC converter, switched-capacitor, hybrid converter 등이 발표되었다.

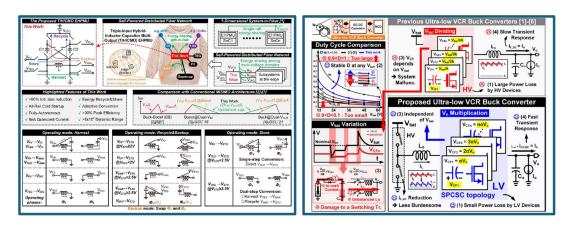

#28.1은 집적 analog LDO를 소개했다. 넓은 주파수 범위에서 높은 PSRR을 얻는 것을 목표로 하였다. LDO 출력이 dominant pole인 경우, 버퍼를 통해 내부 pole을 고주파수로 보내거나 LDO 출력 커패시터를 키워서 stability 확보가 가능하다. 하지만 버퍼를 이용해 내부 pole을 일정 이상의고주파수로 보내는 것은 한계가 있고, 큰 LDO 출력 커패시터를 사용하면 면적이 커지는 문제가

있다. 본 논문에서는 이를 해결하고자 버퍼를 domino 형식으로 직렬 연결하였다. 이를 통해 내부 pole이 여러 개로 분리되고, 이와 동시에 feedforward zero가 추가되어 pole들을 상쇄시킨다. 따라서 내부에는 고주파의 pole 하나만 나타나게 되고, 크지 않은 LDO 출력 커패시터로도 stability 확보가 가능하다. 50 pF의 출력 커패시터를 사용하여 (active area는 0.012 mm²), 10 mA의 로드 전류를 공급한다. 10 kHz까지 -60dB, 1 MHz에서 -36dB, 1 GHz에서 -57dB의 PSRR을 나타낸다.

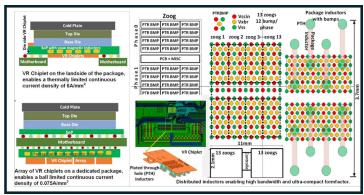

#28.6은 kW 급 SoP (System-on-Package)용 chiplet DC-DC 변환기 기술을 소개했다. 입력은 1.75 V, 출력은 1 V이다. 기존 기술 대비 40배 높은 부하전류 공급이 가능하다. 대전류 공급으로 인한 전력 손실 저감, 열관리, 데이터 송수신 등을 위해 수직 chiplet DC-DC 변환기 기술이 요구된다고소개했다. 해당 변환기는 Ganging을 통해 500 A까지 공급이 가능하며, 52개의 phase, on-package magnetic 인덕터, 16 nm finFET CMOS로 구성된다. 높은 thermal design current (TDC) 확보를 위해단위 zoog를 제어기 기준 대칭적으로 배치했고, 624개의 bump 가 사용됐다. 그 결과, 5년 수명의 200 A의 TDC를 확보했다. Active phase current balancing (PCB) 기술이 적용되었다. Active area는 11·3 mm²이다.

[그림 3] (좌) 높은 PSRR의 LDO <#28.1>, (우) 대전류용 chiplet DC-DC converter <#28.6>

#### 저자정보

#### 정준원 교수

소 속 : 숙명여자대학교 전자공학전공

• 연구분야 : Sensor Readout ICs / Power Management ICs

• 이 메 일 : jwjeong@sookmyung.ac.kr

• 홈페이지: https://sites.google.com/sookmyung.ac.kr/csl